enhancement of test data compression with multistage encoding|Hybrid encoding for test data compression : convenience store A new X-filling algorithm for test power reduction and a novel encoding technique for test data compression in scan-based VLSI testing and efficient decompression . WEB3 de mai. de 2022 · A nossa aluna Catarina Paolino do 3° ano é youtuber e já tem 200 mil seguidores no Tik Tok. Sigam o seu canal: https://youtube.com/c/CatarinaPaolino. A .

{plog:ftitle_list}

Dance Arts Food and Drink Tourism Production and Manufacturing Vehicles and Transportation TikTok Style Athletics Hobbies. Francis Simas (@francissimas1) no TikTok |118 curtidas.627 seguidores.Instagram @francissimas_mastercoach.Assista ao último vídeo de Francis Simas (@francissimas1).

In this paper, we present a hybrid X-filling and two-stage test data compression (TS-TDC) techniques for digital VLSI circuits to reduce the test power and test data volume .In this paper, we present two multistage compression techniques to reduce the test data volume in scan test applications. We have proposed two encoding schemes namely alternating .

This paper presents a unified test data compression approach, which simultaneously reduces test data volume, scan power consumption and test application time .

professionele vochtmeter huren

A new X-filling algorithm for test power reduction and a novel encoding technique for test data compression in scan-based VLSI testing and efficient decompression .Three multistage compression techniques are introduced to reduce the test data volume in scan-test applications. The three encoding schemes namely equal run-length coding . The Combined Compatible block coding and run length coding (CCBRLC) compression algorithm is proposed as to diminish the large test data volume with improved .Ever-increasing test data volume and excessive test power are two of the main concerns of VLSI testing. The ''don't-care'' bits (also known as X-bits) in given test cube can be exploited for .

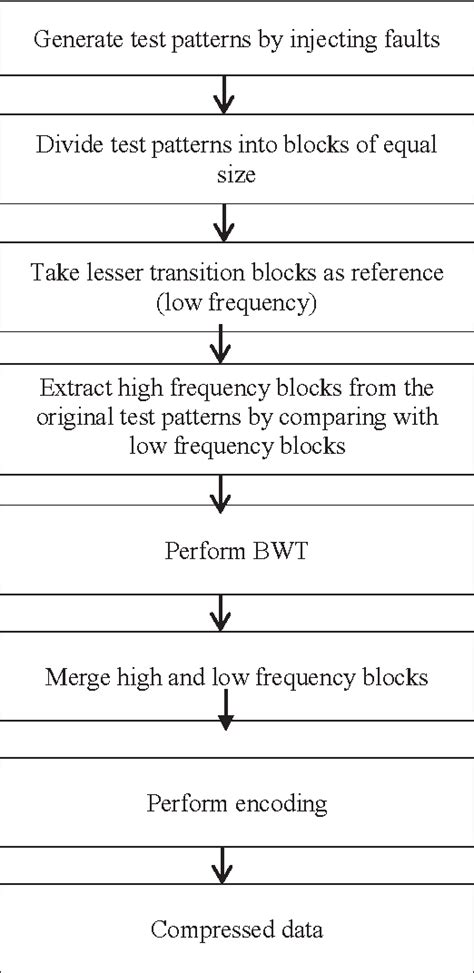

A hybrid test data compression method is presented which is targeted at minimizing the volume of test data, which reduces memory requirements for test data and also time required to test .

TEST DATA COMPRESSION USING MULTISTAGE ENCODING

This paper presents a unified test data compression approach, which simultaneously reduces test data volume, scan power consumption and test application time . A new X-filling algorithm for test power reduction and a novel encoding technique for test data compression in scan-based VLSI testing and efficient decompression architecture is presented to decode the original data with lesser area overhead and power. This paper presents a new X-filling algorithm for test power reduction and a novel encoding technique for test .

Enhancement of test data compression with multistage encoding S. Sivananthama, M. Padmavathyb, Ganga Gopakumarc, P.S. Mallicka,n, J. Raja Paul Perinbamd a School of Electrical Engineering, VIT University, Vellore 632014, Tamil Nadu, India b School of Electronics Engineering, VIT University, Vellore 632014, Tamil Nadu, India c Sankalp and KPIT .In this paper, we present two multistage compression techniques to reduce the test data volume in scan test applications. We have proposed two encoding schemes namely alternating frequency-directed equal-run-length (AFDER) coding and run-length based Huffman coding (RLHC). These encoding schemes together with the nine-coded compression technique .

Data compression techniques are explored in this paper, through which system memory size gets reduced in an effective manner. The size of the memory is always a key constraint in the embedded system.

A new scheme of test data compression based on run-length, namely equal-run-length coding (ERLC) is presented. It is based on both types of runs of 0's and 1's and explores the relationship . A power efficient System-on-a-Chip test data compression method using alternating statistical run-length coding is proposed. To effectively reduce test power dissipation, the test set is firstly preprocessed by 2D reordering scheme. To further improve the compression ratio, 4 m partitioning of the runs and a smart filling of the don’t care bits provide .

These encoding schemes together with the nine-coded compression technique enhance the test data compression ratio. In the first stage, the pre-generated test cubes with unspecified bits are encoded using the nine-coded compression scheme.

DOI: 10.1016/j.vlsi.2013.12.001 Corpus ID: 18752531; Enhancement of test data compression with multistage encoding @article{Sivanantham2014EnhancementOT, title={Enhancement of test data compression with multistage encoding}, author={Sathasivam Sivanantham and M. Padmavathy and Ganga Gopakumar and Partha Sharathi Mallick and J. Raja Paul Perinbam}, . A new scheme of test data compression based on run-length, namely equal-run-length coding (ERLC) is presented. It is based on both types of runs of 0's and 1's and explores the relationship .DOI: 10.1016/j.vlsi.2013.12.001 Corpus ID: 18752531; Enhancement of test data compression with multistage encoding @article{Sivanantham2014EnhancementOT, title={Enhancement of test data compression with multistage encoding}, author={Sathasivam Sivanantham and M. Padmavathy and Ganga Gopakumar and Partha Sharathi Mallick and J. Raja Paul Perinbam}, .

In the second method, the test sets are encoded using nine coded with Alternate variable run length laterally with selective pattern coding to improve the test data compression. Investigational results show that the proposed first and second approaches offer a maximum of 76% and 83% of compression ratio respectively for ISCAS’89 benchmark . Power transition X filling based selective Huffman encoding technique for test-data compression and Scan Power Reduction for SOCs . Enhancement of test data compression with multistage encoding . the proposed encoding schemes exploit the properties of compressed data to enhance the test data compression. This multistage compression is .

professionele vochtmeters

DOI: 10.1016/j.vlsi.2013.12.001 Corpus ID: 18752531; Enhancement of test data compression with multistage encoding @article{Sivanantham2014EnhancementOT, title={Enhancement of test data compression with multistage encoding}, author={Sathasivam Sivanantham and M. Padmavathy and Ganga Gopakumar and Partha Sharathi Mallick and J. Raja Paul Perinbam}, .DOI: 10.1016/j.vlsi.2013.12.001 Corpus ID: 18752531; Enhancement of test data compression with multistage encoding @article{Sivanantham2014EnhancementOT, title={Enhancement of test data compression with multistage encoding}, author={Sathasivam Sivanantham and M. Padmavathy and Ganga Gopakumar and Partha Sharathi Mallick and J. Raja Paul Perinbam}, .DOI: 10.1016/j.vlsi.2013.12.001 Corpus ID: 18752531; Enhancement of test data compression with multistage encoding @article{Sivanantham2014EnhancementOT, title={Enhancement of test data compression with multistage encoding}, author={Sathasivam Sivanantham and M. Padmavathy and Ganga Gopakumar and Partha Sharathi Mallick and J. Raja Paul Perinbam}, . A flexible test-application framework that achieves significant reductions in switching activity during scan shift and the number of specified bits that need to be generated via LFSR reseeding and can significantly reduce the test power and test data volume. This paper presents a new test scheme based on scan block encoding in a linear feedback shift register (LFSR) .

In the second method, the test sets are encoded using nine coded with Alternate variable run length laterally with selective pattern coding to improve the test data compression. Investigational results show that the proposed first and second approaches offer a maximum of 76% and 83% of compression ratio respectively for ISCAS’89 benchmark . A new X-filling algorithm for test power reduction and a novel encoding technique for test data compression in scan-based VLSI testing and efficient decompression architecture is presented to decode the original data with lesser area overhead and power.

Multistage test data compression technique for VLSI circuits

Improvement of test data compression using combined encoding

DOI: 10.1016/j.vlsi.2013.12.001 Corpus ID: 18752531; Enhancement of test data compression with multistage encoding @article{Sivanantham2014EnhancementOT, title={Enhancement of test data compression with multistage encoding}, author={Sathasivam Sivanantham and M. Padmavathy and Ganga Gopakumar and Partha Sharathi Mallick and J. Raja Paul Perinbam}, . Enhancement of test data compression with multistage encoding. Integr. VLSI J. . Power-Aware Testing and Test Strategies for Low Power Devices (2010) S. Arani et al. Multistage encoding for test data compression; L-T. Wang et al. VLSI test principles and architectures; NA Touba ‘Survey of test vector compression techniques. IEEE Des. Test .A new X-filling algorithm for test power reduction and a novel encoding technique for test data compression in scan-based VLSI testing and efficient decompression architecture is presented to decode the original data with lesser area overhead and power. Enhancement of test data compression with multistage encoding. . 2011; TLDR. A novel compatibility-based test data compression method that groups the test vectors that have least incompatible bits and amalgamates them into a single vector by assigning 1 or 0 to unspecified bits and c to incompatible bits that gets a higher compression ratio .

proffesionele vochtmeter voor caravan

It is proven that the data in the P format, regardless of being encrypted, occupies the least amount of storage space among other image formats, that can be easily handled, stored, and shared through clouds and devices safely with a lower cost. Numerous seismic datasets are routinely acquired, stored and transferred via different systems and . A hybrid test data compression method is presented which is targeted at minimizing the volume of test data, which reduces memory requirements for test data and also time required to test the .Characterized by the rapid advancement of artificial intelligence, an abundance of data translates into an expanse of potentialities. Consequently, the challenge of storing large amount of data generated by the long-term operation of the distributed acoustic sensing (DAS) system cannot be ignored in practical applications. Leveraging the nonuniform distribution of quantized spectrum .

It is clearly demonstrated with a large number of experimental results that the proposed scheme improves the test data compression, reduces overall test application time and on-chip area overhead compared to other Huffman code based schemes. A compression-decompression scheme, Modified Selective Huffman (MS-Huffman) scheme based on Huffman code is . A power efficient System-on-a-Chip test data compression method using alternating statistical run-length coding is proposed. . Sivanantham S, Padmavathy M, Gopakumar G et al (2014) Enhancement of test data compression with multistage encoding. . Optimal Selective Count Compatible Runlength Encoding for SOC Test Data .

Hybrid encoding for test data compression

WEBAcompanhantes em Guarujá e garotas de programa. Início. Acompanhantes. São Paulo. Guarujá. en Guarujá. Selecione cidade Guarujá. > Brasil > São Paulo. > Guarujá Para .

enhancement of test data compression with multistage encoding|Hybrid encoding for test data compression